Когда железо перестаёт слушаться расчётов: предсерийные образцы и война с неопределённостью

Инженеры YADRO под микроскопом соединяют эмалированные провода тоньше волоса, чтобы обойти ретаймеры PCIe — и доказывают, что реальность часто не соответствует симуляциям. Почему этап предсерии обходится в 5–10 раз дороже, чем серийная стадия, и как временные доработки помогают избежать месяцев ожи…

Предсерийные образцы: где железо перестаёт слушаться расчётов

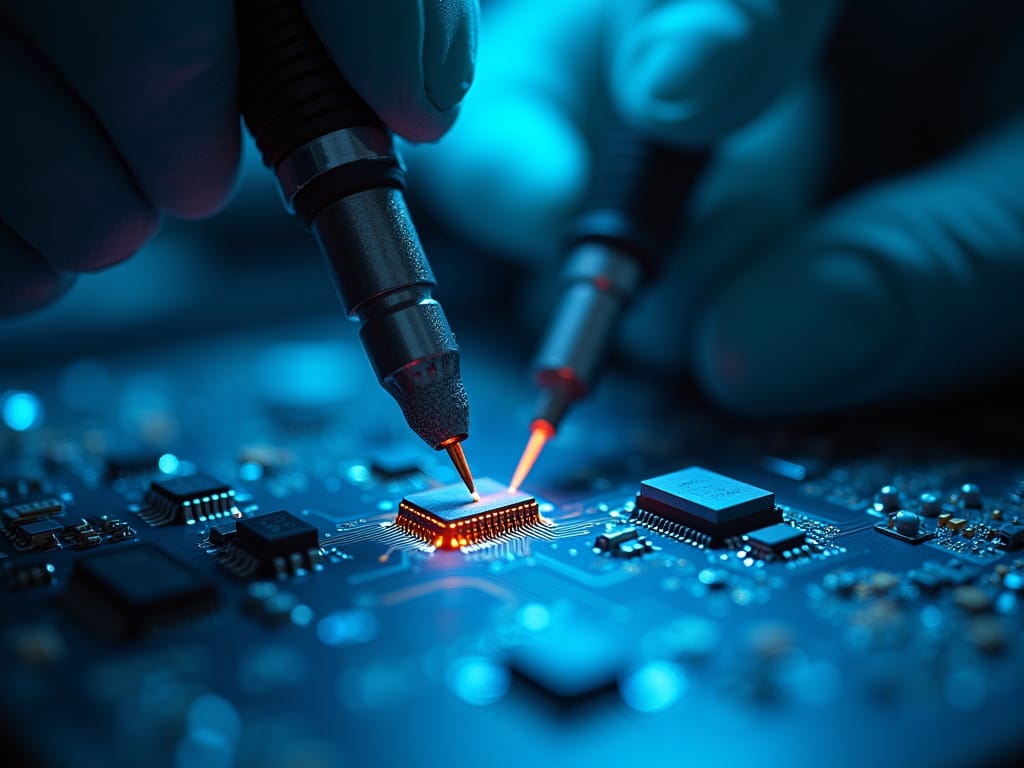

Инженер берёт пинцет, катушку эмалированного провода тоньше волоса и садится за стол с микроскопом. Перед ним четыре платы, на каждой припаяны четыре микросхемы ретаймеров PCIe. Задача — проверить, можно ли убрать эти ретаймеры, которые чинят сигнал на длинных трассах, но добавляют задержку, лишнее тепло и сложность схемы. Под микроскопом он отключает сигнальные линии от микросхем и вручную соединяет 16 дифференциальных пар напрямую. Через день эксперимент завершён: линия PCIe стабильно работает без ретаймеров. Решение позволило избежать нескольких недель ожидания новой ревизии платы.

Цифровые модели и симуляторы не предсказывают таких ситуаций. Они не видят перепутанные дифференциальные пары, не чувствуют термическое повреждение разъёмов и не учитывают износ контактов после десятка пересборок стенда. Предсерийные образцы — это первая точка, где железо начинает диктовать свои условия, а не следовать расчётам. Ошибки, обнаруженные здесь, обходятся в 5–10 раз дороже, чем на серийной стадии. Поэтому этап предсерии — не просто проверка прототипа, а война с иллюзией контроля над процессом разработки.

Отдел сопровождения начинает с воспроизведения бага: включает стенд, запускает прошивку, видит сбой. Дальше — проверка конструктива, прошивок, линий питания, замена компонентов или доработка платы. Прошивки обновляются ежедневно, часть функциональности ещё не реализована, а стандартные инструменты диагностики могут отказать. Иногда проблема не в коде, а в перегреве, пыли или контакте, который просто износился за несколько циклов тестирования. В одном из случаев при диагностике интерконнекта инженеры частично разобрали стенд и обнаружили термическое повреждение и деградацию разъёмов питания — то, чего модели не показывали.

PCIe — это не маркетинговая цифра, а архитектурный ограничитель. Производители обещают PCIe Gen5 с 32 Гбит/с на линию, но реальная пропускная способность зависит от ширины линка, топологии платы, охлаждения и нагрузки. Ошибка в выборе слота или ширины подключения может стать узким местом даже при наличии нового поколения. Например, PCIe 5.0 x4 по пропускной способности примерно соответствует PCIe 4.0 x8. Это значит, что архитектурные решения на этапе предсерии напрямую влияют на будущую производительность системы.

Временные доработки — bodge wires — позволяют проверить инженерные гипотезы за один день вместо нескольких недель. Но у них есть обратная сторона: хаотичность таких исправлений добавляет риски. Если линия не поднимется после пайки, будет сложно понять, где именно ошибка — в проводнике, контакте или схеме. Работа под микроскопом требует ювелирной точности и терпения. Эти доработки — не лень, а вынужденная необходимость, когда стандартные процессы не работают.

Практический вывод прост: если проблема проявляется только на реальном железе, а не в симуляторе, исправление на серийной стадии обойдётся в разы дороже. Предсерийные образцы — это не про «потрогать железо», а про минимизацию рисков и будущих затрат. Каждая доработка и каждый отказ здесь — это обратная связь, которая делает продукт стабильным. Инженеры, работающие с предсерийными образцами, не чинят железо — они воюют с неопределённостью, где реальность не соответствует модели.